Is it possible to use a 4 lane MIPI DSI display with the STM32? The STM32 DSI host only has 2 data lanes.

Yes, and no!

In this article, we go into the details of what displays can and cannot be used with the STM32 MIPI DSI host. It is not as simple as picking up any MIPI DSI display and whacking it on to the STM32.

If the MIPI DSI display has 4 lanes, there may or may not be support for a 2 lane DSI host.

Read on for a definitive guide.

However, if you are just looking for a display interface that uses fewer lines to connect to the panel, using STM32 with LVDS displays may be your solution (LVDS systems use a full parallel RGB interface and a serializer chip – not a pin and power saver like DSI is!).

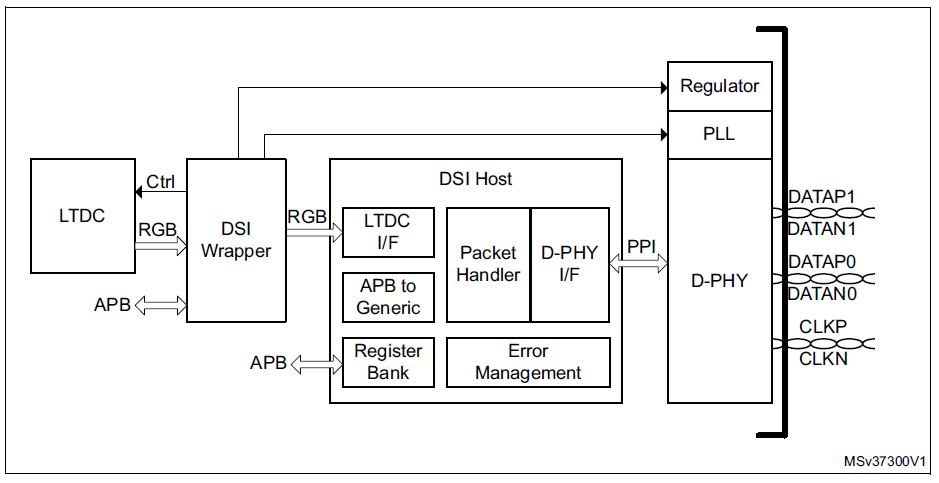

STM32 MIPI DSI data lanes

The number of data lanes in the MIPI DSI interface physical link are important. When you look at number of lanes on the DSI interface, you should think of them as unique but interchangeable (usually) data lines.

Just like you can swap out data lines on DDR, you can usually swap out lanes in the DSI host to display interface. However, a mismatch in the number of lanes needs to be resolved depending on the display module controller.

Every STM32 that features a MIPI DSI host has a pair of differential clock lines (CLK0_P and CLK0_N). This clock pair can put out a maximum clock rate of 500 MHz, which results in the data lanes (DATA0 and DATA1 pairs) shifting out data at 1 Gbps each.

The MIPI Alliance specifications do not specify a maximum resolution or frame rate. It is up to you to negotiate and decide that with the display attached to the DSI host.

Also, because control traffic is also carried by the MIPI DSI interface itself, you have to make sure that there is no significant control traffic interrupting the graphic data stream. If there is, the display benefits from having a frame buffer. Ultimately, depending on the timing parameters specified in the LCD display datasheet, the maximum resolution and frame rate can be determined and it strongly depends on the display controller.

Note that the STM32 DSI host is capable of halting transmission, i.e. if your display has a frame buffer, you can save some power by deactivating constant streaming of the video buffer through the DSI host. If you are interfacing to an non-framebuffer type display, it could be a good idea to allocate the display data into external SDRAM connected to the STM32 and let the LTDC stream it out to the LCD via the MIPI DSI host interface.

Using a 4 lane MIPI DSI display with 2 lane DSI host

As noted in the section above, the DSI host is only responsible for pumping data out. How much data can be pumped out is limited by the slower party (DSI host or slave).

Having 4 lanes allows for transferring larger amounts of data using the same lane clock speed.

This means that using 2 lanes should be fine, even though the application will take a hit in terms of maximum framerate (assuming the resolution stays the same).

So now that we know that the DSI physical layer has no issue with you swapping out lanes or using only some of the lanes, this is just what the standard prescribes.

Many high resolution display manufacturers prefer using 4 lanes so that the clock rate will not have to be ridiculously high to support a high frame rate. Let us take a look at the practical considerations.

When is a 4 lane MIPI DSI compatible with a 2 lane host?

The answer to this question resides in the display controller datasheet only.

Many MIPI DSI displays will allow you to set the lane configuration. The lane configuration is usually set in the LCD controller using a combination of hardware pins and register settings.

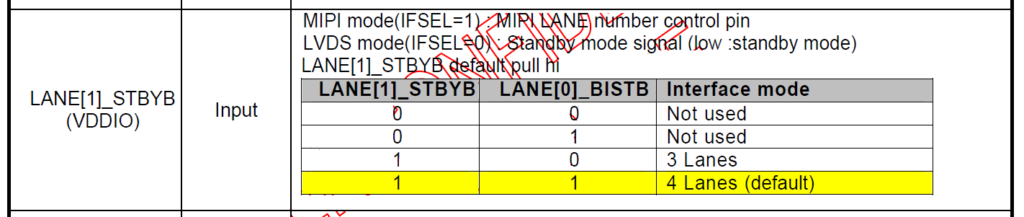

For example, here is a look at a 1024×768 LCD controller that only supports 3 or 4 DSI data lanes.

It is clear that 1 lane and 2 lane configurations are marked as unused and so there is no way to make this display controller work with the STM32 DSI host.

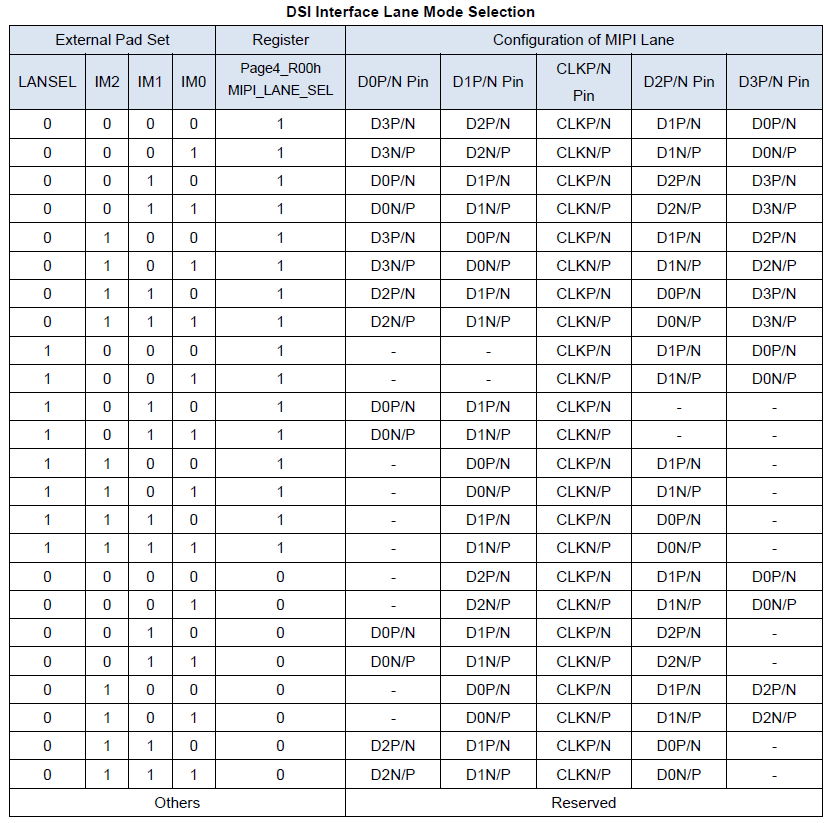

On the other hand, there are displays that let you use any number of lanes in any configuration of your choice.

For example, here is a display controller for 1280×800 LCD displays that lets you configure the lanes in any way you want to, including all lane swapping configurations to make PCB layout easy. This controller lets you use 2, 3, or 4 data lanes.

So it is clear at this point that the display controller reserves the right to decide what lanes it wants you to use and whether or not it will allow lane swapping.

Practical considerations

Now that we have seen that LCD controllers exist that can drive a 1024×800 LCD display and also allow for using any number of lanes between 2 to 4. Even if you compromised on the frame rate to use 2 lanes only for driving a 1024×768 display, can you actually do it?

Unfortunately, from our years of design experience we have very rarely seen displays which have 4 lanes and also have lane configuration pins for the LCD controller exposed. In the example lane configuration table above, you might have observed that the controllers tend to set lane count using physical IOs.

An LCD module manufacturer will simply hardwire these IOs to make the controller always use 4 lane mode. Therefore, there is nothing you can do to make the controller use 2 DSI data lanes instead of 4 DSI data lanes.

There are many such MIPI DSI LCD displays that contain a 2-lane compatible controller but the lane count setting pins are simply not available for you to set.

Final verdict

So all things considered, including the STM32 series, MIPI Alliance specifications and practical availability of LCDs in the market, here is what we can conclude.

Resolutions under 800 x 480

It is possible to interface these displays to STM32 MIPI DSI host.

Most LCD display manufacturers will have 2 lanes on a display of this resolution so you can hook these up to the STM32 (provided that the DSI data format and timing is compatible).

Resolutions higher than 800 x 480

It is not possible to interface these displays to the STM32 MIPI DSI host. There just are not enough LCD displays in the market that are higher resolution than 800×480 and still support 2 data lanes.

It is possible, however, to interface LCD displays of resolution up to 1280 x 800 with a 2 data DSI host. We know compatible controllers exist, but this will most likely involve asking the LCD panel manufacturer to change the LCD controller configuration. We know that it is only possible for high volume applications, otherwise the LCD manufacturers are not usually interested.

Display size smaller than 5"

It is easily possible to interface a display smaller than 5″ in size with the STM32 MIPI DSI host. Assuming that the display resolution is a maximum of 800 x 480, there are many displays that will support 2 data lanes.

Display size larger than 5"

It can be difficult to find displays larger than 5″ in size and of resolutions equal to or smaller than 800 x 480. Therefore is it hard to find displays larger than 5″ in size that can support 2 DSI data lanes with the STM32. Remember than the DSI interface is most popular with phones and small, low power consumer devices.

Larger displays will tend to use LVDS (4 data lanes), which can be interfaced with an STM32. LVDS is whole another subject and we might cover it in another article in the future.

An Alternative Approach

There are still some situations where you are forced to use MIPI DSI interface. For example, AMOLED displays with relatively low resolutions exclusively use 4-lane MIPI DSI interface only. So do many smartphone-size display panels which have astonishing clarity and color depth for their price point.

In a case like this, a potential solution could be to use an RGB to MIPI DSI bridge. While this adds cost to your design and takes away a lot of GPIOs, you can still have your way with a 4-lane display using any MCU that has a simple RGB parallel TFT LCD interface peripheral.

Please fill in the Subscription Form in the sidebar so we can keep you updated with our latest articles.

We only mail you less than 2 times a month.

Change Log

- Initial Release: 04 March 2021

References

- Reference 1: STM32H747 Datasheet

- Reference 2: STM32H747 User Manual

- Reference 3: Confidential Ilitek LCD controller datasheets

- Reference 4: EK79030 MIPI DSI LCD controller datasheet

3 comments

Hello, very interesting !

Normally we can use 7” lcd raspberry DSI (800×480) on stm32F769i-disoc / stm32H745-disco (DSI 4” 800×480)’.

We need to use ST adaptor B-LCDAD-RPI1.

I just receive parts (very nice screen), but lcd dsi 7” don’t run at this moment, nothing with standard 4” software touchgfx configuration.

If someone find how to … let me know ;-)

We are actually planning on placing custom orders for 1024×768 or similar 7″ LCD that supports a 2 lane MIPI DSI interface with capacitive touch.

A display like that is near impossible to find, so it could be useful for embedded applications. Many other application processors with cortex-A series cores that run Linux also have a 2-lane MIPI DSI port.

Today 800×600 7” is enough Ok but why not more :-)

However, in addition to the hardware, the software configuration must be applied.

(I want to continue working with the ST disco DSI cards)

Let me know if you have a solution, and if you propose another LCD.

Thanks!